Rugged FMC ADC cards built to ANSI/VITA 57.1 for high-speed, high-reliability signal digitization. Engineered for defense, radar, EW and mission-critical data acquisition in harsh environments.

FMC ADC Cards

Rugged FMC ADC cards built to ANSI/VITA 57.1 for high-speed, high-reliability signal digitization. Engineered for defense, radar, EW and mission-critical data acquisition in harsh environments.

All FMC mezzanine cards comply with standard FMC interfaces and are compatible with upcoming carrier boards and development platforms.

Below is a summary of key specifications to help you select the right model quickly.

Product Selection Table

Part Number | Function Type | FMC Standard | Form Factor | Channel Count | Resolution | Sampling Rate | Port | FMC Connector | Temp. Range |

| EL11FMC00A002 | ADC | FMC1.0 (VITA 57.1) | Single Width | 1 or 2 | 12-bit | 6.4 GSPS / 3.2 GSPS | SSMA*4 | HPC | -40℃~ +85℃ |

| EL11FMC00A003 | ADC | FMC+ (VITA 57.4) | Single Width | 1 or 2 | 12-bit | 10.4 GSPS / 5.2 GSPS | SSMA*4 | HSPC | -40℃~ +85℃ |

| EL11FMC00A004 | ADC | FMC1.0 (VITA 57.1) | Single Width | 8 | 16-bit | 256 MSPS | SSMC*10 | HPC | -40℃~ +85℃ |

| EL11FMC00A007 | ADC | FMC1.0 (VITA 57.1) | Single Width | 2 | 16-bit | 3 GSPS | MCX*4 | HPC | -40℃~ +85℃ |

| EL11FMC00A011 | ADC | FMC1.0 (VITA 57.1) | Dual Width | 8 | 14-bit | 2 GSPS | SSMC*12 | HPC+ HSPC | -40℃~+85℃ |

| EL11FMC00A015 | ADC | FMC+ (VITA 57.4) | Single Width | 2 or 4 | 12-bit | 6.4 GSPS / 3.2 GSPS | SSMA*6 | HSPC | -40℃~+85℃ |

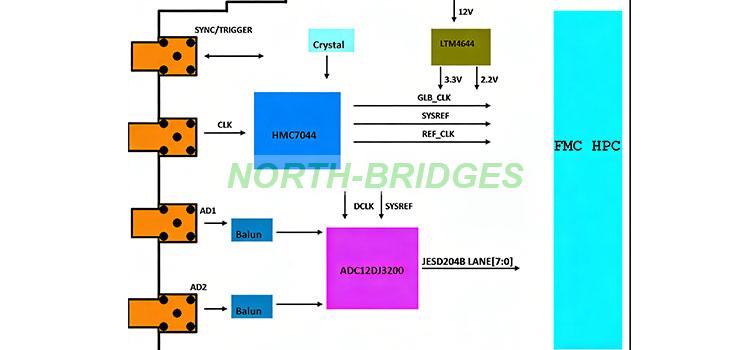

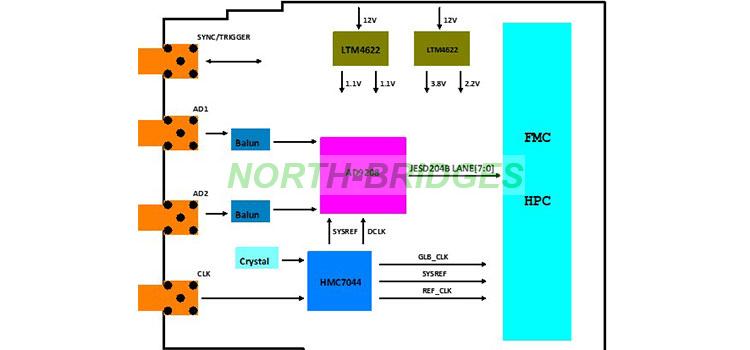

Product No.: EL11FMC00A002

12‑Bit Single 6.4 GSPS / Dual 3.2 GSPS ADC FMC Mezzanine Card

Key Features

The EL11FMC00A002 is a high‑performance FMC mezzanine card with ADC supporting dual 3.2 GSPS or single 6.4 GSPS sampling.

It integrates an HMC7044 clock generator for JESD204B timing, supports synchronization and triggering, and uses SSMA RF connectors.

Fully compliant with VITA 57.1, the module is ideal for communications, radar, test instrumentation, ATE and industrial automation.

Specifications

| ADC: | ADC12DJ3200, 12-bit, 3.2 GSPS (dual) / 6.4 GSPS (single) | ||||||||

| Direct RF sampling: | Direct RF sampling covering I/S/C/X‑band for frequency‑agile systems | ||||||||

| Interface: | 8‑lane JESD204C, up to 12.8 Gbps SerDes | ||||||||

| Noise Floor: | –151.8 dBFS/Hz (dual), –154.4 dBFS/Hz (single) | ||||||||

| Analog Bandwidth: | 8.0 GHz (–3 dB), Default VFS: 0.8 Vpp | ||||||||

| Optional DDC: | 4× / 8× complex decimation filtering | ||||||||

| Clock: | HMC7044 + onboard TCXO; internal / external reference, software‑selectable | ||||||||

| General: | 4× SSMA, VITA 57.1 compliant, HSPC connector, internal/external trigger | ||||||||

| Dimensions: | 84.1 mm × 69 mm | ||||||||

| Temp: | –40 °C to +85 °C | ||||||||

Block Diagram

Applications

Communications, Radar Systems, Test & Measurement, ATE, Industrial Automation

Ordering

| PN: | EL11FMC00A002 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

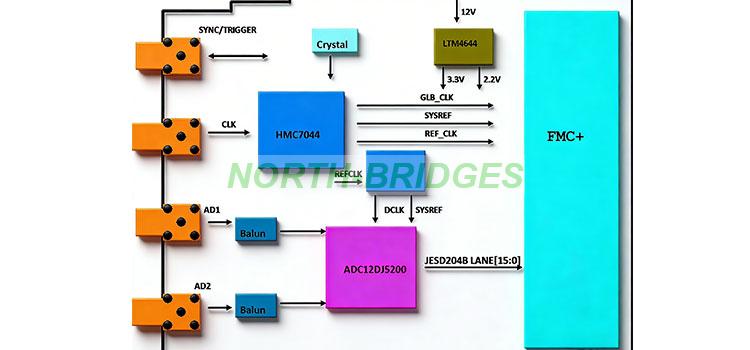

Product No.: EL11FMC00A003

12 Bit Single 10.4 GSPS / Dual 5.2 GSPS ADC FMC+ Mezzanine Card

Key Features

EL11FMC00A003 is a high-performance FMC+ mezzanine card with a high-speed ADC: 10.4 GSPS (single-channel) or 5.2 GSPS (dual-channel). It integrates HMC7044/LMX2594 clock ICs for stable JESD204C clock signals, with SSMA RF connectors for analog I/O, synchronization/trigger functions, VITA 57.4 compliance, and applicability to communications, radar, test & measurement, ATE, and industrial automation.

Specifications

| ADC Specifications | |||||||||

| Model: | ADC12DJ5200 (backward compatible with ADC12DJ4000/ADC12DJ3200) | ||||||||

| Sampling Rate: | 5.2 GSPS (dual); 10.4 GSPS (single) | ||||||||

| Resolution: | 12 bits | ||||||||

| RF Sampling: | Direct I/S/C/X-band (frequency-agile) | ||||||||

| Interface: | 16-lane JESD204C | ||||||||

| SerDes: | Up to 17.16 Gbps | ||||||||

| Encoding: | 8B/10B (JESD204B compatible) & 64B/66B | ||||||||

| Noise Floor (-20 dBFS, VFS=1.0 Vpp-diff): | Dual: -151.8 dBFS/Hz; Single: -154.4 dBFS/Hz | ||||||||

| Analog Bandwidth (-3 dB): | 8.0 GHz | ||||||||

| VFS (default): | 0.8 Vpp | ||||||||

| Optional DDC: | 4×/8× complex decimation | ||||||||

| Clock Specifications | |||||||||

| ICs: | HMC7044 & LMX2594 | ||||||||

| Clock Source: | On-board/external (software-selectable) | ||||||||

| General Specifications | |||||||||

| Analog I/O: | 4× SSMA | ||||||||

| Form Factor: | FMC+ (VITA 57.4) | ||||||||

| Connector: | HSPC | ||||||||

| Trigger: | Internal/external | ||||||||

| Dimensions: | 84.1×69 mm | ||||||||

| Temp: | -40~+85°C (industrial) | ||||||||

Block Diagram

Applications

Communications, Radar Systems, Test & Measurement, ATE, Industrial Automation

Ordering

| PN: | EL11FMC00A003 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

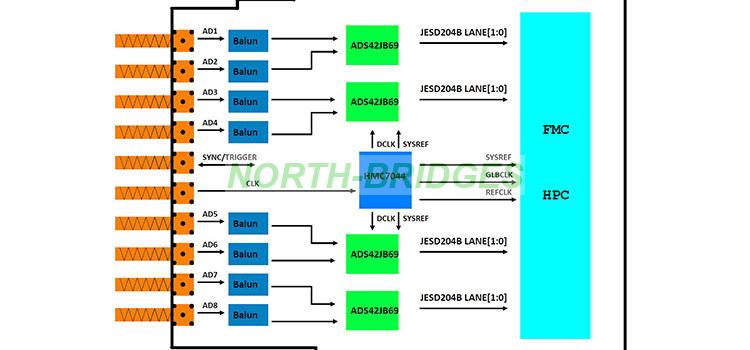

Product No.: EL11FMC00A004

8-Channel 16-Bit 256 MSPS ADC FMC Mezzanine Card

Key Features

The EL11FMC00A004 is a JESD204B-based 8-channel, 250 MSPS, 16-bit synchronous ADC FMC mezzanine card. It boasts 16-bit resolution and max 250 MSPS sampling rate, integrating HMC7044 clock management IC (supports on-board/external clock reference). Adopting TI’s ADS42JB69 ADC with low power consumption and superior dynamic performance, it is ideal for multicarrier broadband communication and high-sampling-rate, high-precision ADC scenarios.

Specifications

| ADC Specifications | |||||||||

| ADC Model: | ADS42JB69 | ||||||||

| Configuration: | 8-channel, 16-bit, 250 MSPS | ||||||||

| Input Coupling: | AC-coupled | ||||||||

| Package: | 9mm×9mm QFN64 | ||||||||

| SFDR @170MHz: | 85 dBc | ||||||||

| SNR @170MHz: | 74.7 dBFS | ||||||||

| ENOB @170MHz: | 12 bits | ||||||||

| Analog Input Range: | 2.5 Vpp | ||||||||

| Clock Management | |||||||||

| Clock IC: | HMC7044 | ||||||||

| Clock Reference: | On-board/external, software-selectable | ||||||||

| General Specifications | |||||||||

| Analog I/O Connectors: | SSMC | ||||||||

| Form Factor: | Standard FMC, fully compliant with VITA 57.1 | ||||||||

| Trigger Modes: | Internal/external | ||||||||

| Board Dimensions: | 84.1mm×69mm | ||||||||

| Power Consumption: | 9 W | ||||||||

| Operating Temp: | -40 °C to +85 °C | ||||||||

Block Diagram

Applications

Multicarrier Broadband Communication; High-sampling-rate, high-precision ADC scenarios

Ordering

| PN: | EL11FMC00A004 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | Available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

Product No.: EL11FMC00A007

2-Channel 16-Bit 3 GSPS ADC FMC Mezzanine Card

Key Features

Adopts AD9208 low-power, wide-bandwidth 16-bit 3 GSPS ADC, supports JESD204B high-speed serial interface (up to 15 Gbps). AD9208 is backward compatible with AD9689, delivering excellent spurious-free dynamic range over wide input frequency with ultra-low power. Equipped with HMC7044 clock management IC, supporting external and onboard clock modes. Suitable for electronic test/measurement, phased-array radar, electronic warfare (EW).

Specifications

| ADC Specifications | |||||||||

| Model: | (backward compatible with AD9689) | ||||||||

| Configuration: | 2 channels, 14-bit resolution, 3 GSPS max sampling rate | ||||||||

| Input Impedance: | 50 Ω | ||||||||

| Full-Power Bandwidth: | 9 GHz | ||||||||

| Channel Isolation/Crosstalk: | 100 dBc @ 170 MHz | ||||||||

| Data Interface: | 8-lane JESD204B | ||||||||

| Clock Specifications | |||||||||

| Clock IC: | HMC7044 | ||||||||

| Clock Reference: | On-board/external, software-selectable | ||||||||

| General Specifications | |||||||||

| Analog I/O: | 4× MCX connectors | ||||||||

| Form Factor: | Standard FMC, fully compliant with VITA 57.1 | ||||||||

| Trigger Modes: | Internal/external | ||||||||

| Dimensions: | 84.1 mm × 69 mm | ||||||||

| Operating Temp: | −40 °C to +85 °C | ||||||||

Block Diagram

Applications

Electronic Test and Measurement Systems, Phased-Array Radar Systems, Electronic Warfare (EW).

Ordering

| PN: | EL11FMC00A007 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | Available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

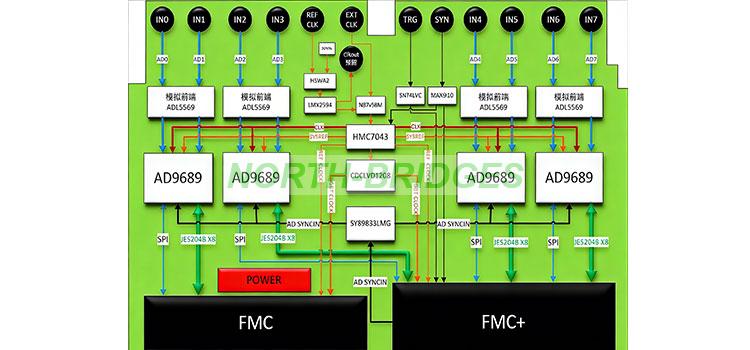

Product No.: Product EL11FMC00A011

Dual-Width 8-Channel 14-Bit 2 GSPS ADC FMC & FMC+ Mezzanine Card

Key Features

Dual-wide FMC/FMC+ mezzanine card, 8-channel 14-bit ADC, 2 GSPS per channel, 8 GHz (-3 dB) full-power analog input bandwidth.

Based on ADI AD9689BBPZ-2000 ADC; supports trigger I/O, 3 clock/reference configurations (internal/external reference, external clock), SPI-configurable clock selection.

External synchronization for multi-channel ADC; compliant with ANSI/VITA 57.1/57.4 (electrical/mechanical).

Interfaces to FPGA carrier via HPC/HSPC high-speed connectors; 12 SSMC coaxial front-panel I/O.

Air/conduction-cooled; enables 8-channel simultaneous sampling with compatible carrier card.

Specifications

| Sampling Rate: | 2 GSPS | ||||||||

| Channel Configuration: | 8 channels (4 ADC devices) | ||||||||

| Input Coupling: | AC/DC selectable (AC default) | ||||||||

| Resolution: | 14 bits | ||||||||

| Full-Power Bandwidth (-3 dB): | 8 GHz | ||||||||

| Synchronization: | External sync supported | ||||||||

| Digital Interface: | JESD204B | ||||||||

| Mechanical & Electrical Standard: | VITA 57.1 | ||||||||

| Cooling: | Air/conduction-cooled | ||||||||

| Clock & Reference Sources: | Internal/external clock, external reference | ||||||||

| Connectors: | HPC + HSPC high-pin-count | ||||||||

| Front Panel I/O: | 12 SSMC coaxial connectors | ||||||||

Block Diagram

Applications

Software Defined Radio (SDR), Digital Beamforming (DBF), Electronic Warfare (EW) for Radar/Sonar

Wireless Communications, High-Speed Data Acquisition/Playback, Test & Measurement Instruments

Ordering

| PN: | EL11FMC00A011 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | Available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

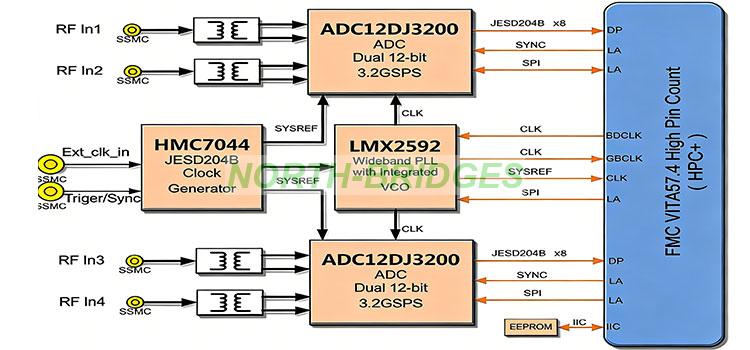

Product No.: EL11FMC00A015

12‑Bit Dual 6.4 GSPS / Quad 3.2 GSPS ADC FMC+ Mezzanine Card

Key Features

This 12-bit FMC+ AD acquisition module supports 4-channel 3.2GSPS or 2-channel 6.4GSPS sampling, fully compliant with VITA 57.4. It acts as a high-performance front-end I/O module for FPGAs, with a 16-lane JESD204B interface linking to FPGA GTH transceivers via the FMC+ connector. It supports on-board programmable sampling clocks and external reference clocks, and enables multi-module synchronous acquisition via trigger I/O. Four analog inputs use 50Ω SSMC RF connectors with AC transformer coupling.

Specifications

| ADC Specifications | |||||||||

| JESD204B (Subclass 1) digital output, up to 16Gbps/lane | |||||||||

| Power consumption: | 1.65W @ 3GSPS | ||||||||

| SNR: | 57.2dBFS @2.6GHz, -2dBFS; 59.5dBFS @2.6GHz, -9dBFS | ||||||||

| SFDR: | 70dBFS @2.6GHz, -2dBFS;78dBFS @2.6GHz, -9dBFS | ||||||||

| Integrated input buffer | |||||||||

| Noise density: | -152dBFS/Hz | ||||||||

| Core supplies: | 0.975V, 1.9V, 2.5V | ||||||||

| Analog input BW (-3dB): | 9GHz | ||||||||

| Dual integrated wideband digital processors with 48-bit NCO | |||||||||

| Flexible JESD204B lane config | |||||||||

| Clock Specifications | |||||||||

| External sampling clock | |||||||||

| External reference clock: | 10/20MHz, -2~10dBm@50Ω, MMCX | ||||||||

| General Specifications | |||||||||

| FMC+ compliant (VITA 57.4) | |||||||||

| Dimensions: | 78mm×69mm | ||||||||

| Connector: | ASP-184330-01 HPC | ||||||||

| Power input: | +12V | ||||||||

| I²C control interface supported | |||||||||

| External trigger I/O | |||||||||

| Power: | 1A max @+3.3V (±5%) | ||||||||

| Cooling: | natural air cooling | ||||||||

| Operating temp: | -40°C~+85°C | ||||||||

| Storage temp: | -55°C~+125°C | ||||||||

| Humidity: | 5%~95% non-condensing | ||||||||

Block Diagram

Applications

Radar & smart antennas, EW, test & measurement, SDR

Ordering

| PN: | EL11FMC00A015 | ||||||||

| Lead time: | Inquire for official quotation | ||||||||

| Custom designs: | Available upon request | ||||||||

| Support: | FPGA reference design, schematic review, driver development (quoted separately) | ||||||||

Contact: Windy Lian

Phone: 13862120662

E-mail: sales@north-bridges.com

Whatsapp:

Add: Suzhou City, China

We chat